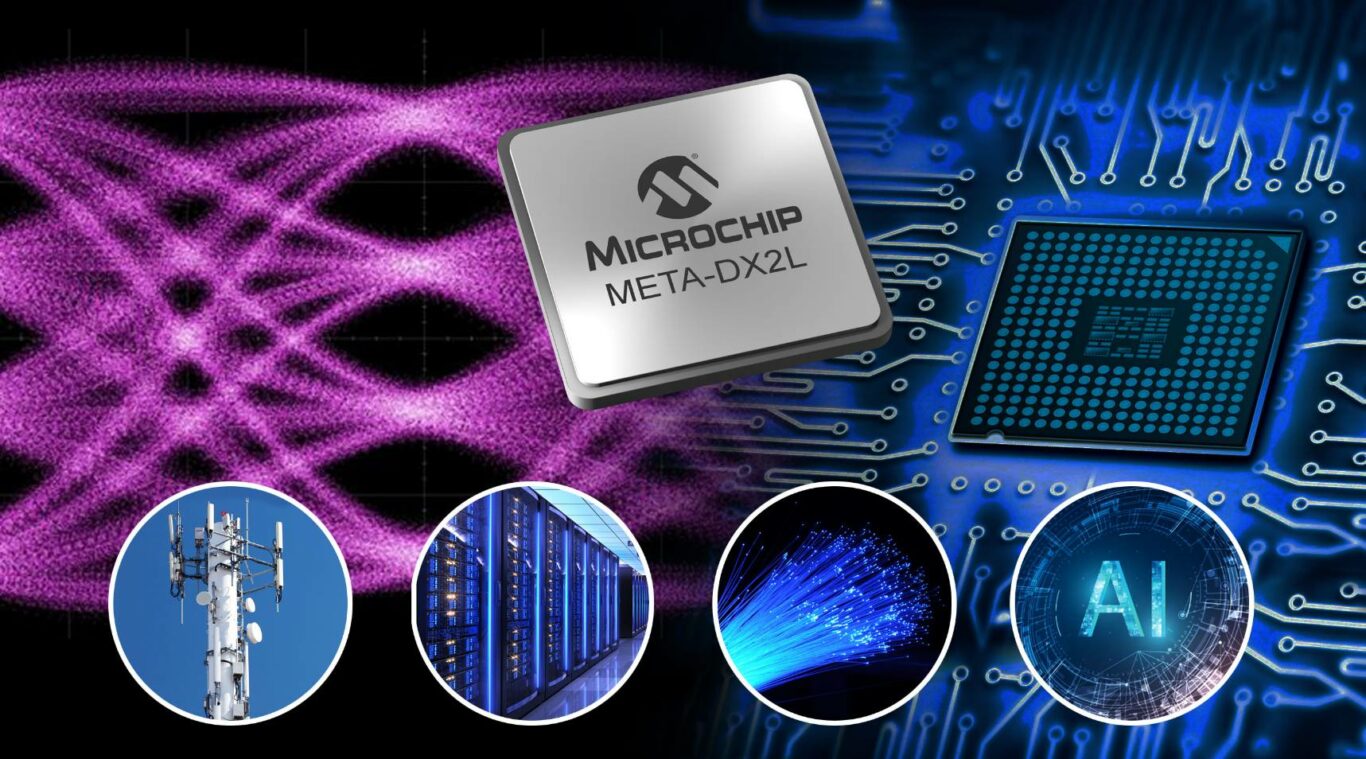

ไมโครชิพ เปิดตัว Ethernet PHY 1.6T ขนาดกะทัดรัดที่สุดในอุตสาหกรรม เชื่อมต่อสูงถึง 800 GbE ไปยังศูนย์ข้อมูลคลาวด์ด้วย 5G และ AI META-DX2L ช่วยให้ เราเตอร์ สวิตช์ และไลน์การ์ดเพิ่มแบนด์วิดธ์เป็นสองเท่าโดยเปลี่ยนการทำงาน ด้วยอัตราอินเทอร์เฟซ 112G PAM4

9 กันยายน 2564 — การรับส่งข้อมูลไปยังศูนย์ข้อมูลที่เพิ่มสูงขึ้นผ่านระบบ 5G บริการคลาวด์รวมถึงแอปพลิเคชัน ที่ใช้งาน Artificial Intelligence (AI) และ Machine Learning (ML) นั้น ส่งผลทำให้อุปกรณ์เราเตอร์ สวิตช์ และไลน์การ์ด (line cards) ต้องใช้แบนด์วิดธ์ที่สูงขึ้น รวมถึงความถี่ของพอร์ตและการเชื่อมต่อสูงถึง 800 Gigabit Ethernet (GbE) เช่นกัน แต่การเปลี่ยนแปลงที่จะทำให้แบนด์วิดธ์สูงขึ้นได้ จำเป็นต้องอาศัยการออกแบบอุปกรณ์ที่สามารถตอบสนองต่อความท้าทายเรื่องเสถียรภาพของการรับส่งสัญญาณ ดังนั้นการเชื่อมต่ออุปกรณ์ที่มีในอุตสาหกรรมปัจจุบันจึงต้องถูกปรับให้เชื่อมต่อกับ PAM4 Serializer/Deserializer (SerDes) แบบ 112G (กิกะบิตต่อวินาที) ซึ่งสามารถรองรับออปติกแบบเสียบ (pluggable optics) แบ็คเพลน (backplanes) ของระบบ และแพ็กเก็ต โปรเซสเซอร์แบบล่าสุดได้ ความท้าทายเหล่านี้สามารถแก้ปัญหาได้ด้วยการใช้ PHY (physical layer) พลังงานต่ำ 1.6T (เทราบิตต่อวินาที) ที่มีขนาดกะทัดรัดที่สุดในอุตสาหกรรมจาก Microchip Technology Inc. (Nasdaq: MCHP) อุปกรณ์ PM6200 META-DX2L ที่ลดพลังงานต่อพอร์ตลงร้อยละ 35 เมื่อเทียบกับรุ่น 56G PAM4 ที่ออกมาก่อนหน้านี้ ดังนั้น META-DX1 จึงถือเป็นโซลูชัน PHY ระดับเทราบิตชิ้นแรกของอุตสาหกรรม

“อุตสาหกรรมกำลังเปลี่ยนไปใช้ระบบแบบ 112G PAM4 สำหรับการสลับสัญญาณที่มีความถี่สูง การประมวลผลแพ็กเก็ต และ optics” นอกจากนี้ Bob Wheeler นักวิเคราะห์หลักด้านเครือข่ายที่ The Linley Group ยังได้กล่าวอีกว่า “META-DX2L ของไมโครชิพได้รับการปรับปรุงให้ตอบสนองความต้องการเหล่านี้ โดยเชื่อมการทำงานกับ line cards เพื่อสลับแฟบริก (fabrics) และ multi-rate optics สำหรับการเชื่อมต่อแบบ 100 GbE 400 GbE และ 800 GbE”

ด้วยความถี่ของแบนด์วิดธ์ที่เพิ่มสูงขึ้นเป็น 1.6T ประหยัดพื้นที่ ใช้งานกับเทคโนโลยี 112G PAM4 SerDes และรองรับอัตราการส่งสัญญาณของ Ethernet ตั้งแต่ 1 ถึง 800 GbE ทำให้อุปกรณ์ META-DX2L Ethernet PHY ของไมโครชิพถือเป็นเครื่องมือระดับอุตสาหกรรมที่มีความสามารถ ในการเชื่อมต่อที่หลากหลายนำไปประยุกต์ในการออกแบบเพื่อนำอุปกรณ์ต่างๆกลับมาใช้ใหม่ได้อย่างมีประสิทธิภาพสูงสุด เช่น รีไทม์เมอร์ กระปุกเกียร์ หรือกระปุกเกียร์ถอยหลัง ไปจนถึง multiplexor (mux) 2: 1 ที่ไม่ทำงาน เป็นต้น จากตัวอย่างที่กล่าวไปข้างต้น คุณลักษณะของครอสพอยท์และกระปุกเกียร์ที่กำหนดค่าได้สูงขึ้น ส่งผลทำให้อุปกรณ์ใช้งานแบนด์วิดท์ I/O ของสวิตช์ได้อย่างเต็มกำลัง จนทำให้สามารถเปิดใช้งานการเชื่อมต่อที่ยืดหยุ่นซึ่งจำเป็นสำหรับการทำงานของ multi-rate cards ที่รองรับ pluggable optics ได้หลากหลายรูปแบบ

นอกจากนี้ PAM4 SerDes ที่ใช้พลังงานต่ำของ PHY ยังช่วยให้อุปกรณ์สามารถรองรับอัตราอินเทอร์เฟซสำหรับโครงสร้างพื้นฐานของ cloud data center คลัสเตอร์ประมวลผล AI/ML และ 5G ในอนาคตได้อีกด้วย รวมถึงโครงสร้างพื้นฐานของผู้ให้บริการโทรคมนาคม ไม่ว่าจะใช้สายเคเบิล ทองแดงแบบเชื่อมต่อโดยตรงระยะไกล (Direct Attach Copper) backplanes หรือการเชื่อมต่อกับ pluggable optics

“สำหรับรุ่น 56G เราได้เปิดตัว PHY เทราบิตรุ่นแรกของอุตสาหกรรมในชื่อว่า META-DX1 และตอนนี้เราได้ขยายขอบเขตไปพัฒนาคุณสมบัติของ 112G ซึ่งตอบโจทย์นักพัฒนาระบบในการใช้แก้ปัญหาความท้าทายใหม่ ๆ ที่เกิดจาก cloud data centers เครือข่าย 5G และ การขยายขนาดการประมวลผลของ AI/ML” นอกจากนนี้ Babak Samimi รองประธานหน่วยธุรกิจการสื่อสารของไมครชิพได้ขยายความเพิ่มว่า “ถึงแม้ว่าจะรับส่งสัญญาณผ่านแบนด์วิดธ์ด้วยความถี่สูงถึง 1.6T โครงสร้างภายของอุปกรณ์จะใช้พลังงานต่ำและมีขนาดที่เล็กที่สุด อุปกรณ์ META-DX2L PHY จะเพิ่มแบนด์วิดธ์เป็นสองเท่าเมื่อเทียบกับอุปกรณ์อื่นๆที่ออกมาก่อนหน้านี้ในท้องตลาด ที่สำคัญอุปกรณ์ตัวนี้จะสร้างมาตรฐานใหม่ สำหรับประสิทธิภาพในการประหยัดพลังงาน”

META-DX2L ถูกผลิตมาในขนาดบรรจุภัณฑ์ที่เล็กที่สุดในอุตสาหกรรม 23 x 30 มม. (มม.) ซึ่งช่วยให้ประหยัดพื้นที่ ซึ่งมีความจำเป็นในการสร้าง ความหนาแน่นของพอร์ต line card สำหรับไฮเปอร์สเกลเลอร์และนักพัฒนาระบบ ไฮไลท์ของผลิตภัณฑ์ มีดังนี้

• อุปกรณ์คู่ 800 GbE, Quad 400 GbE และ 16x 100/50/25/10/1 GbE PHY

• รองรับอัตราการรับส่งข้อมูลผ่าน Ethernet OTN และ Fibre Channel

• รองรับอัตราการรับส่งข้อมูลสำหรับแอปพลิเคชันที่ใช้ AI/ML

• มี mux hitless แบบ 2:1 ในตัว โครงสร้างภายในมีความพร้อมใช้งาน/การป้องกันสูง

• ครอสพอยท์ที่กำหนดค่าได้สูงรองรับบริการหลายอัตราบนพอร์ตอื่น ๆ

• ระยะแฝงคงที่ เปิดใช้งาน IEEE 1588 Class C/D PTP ที่ระดับการตั้งค่ามาตรฐานของระบบ

• การยกเลิก การตรวจสอบ และการแปลง FEC ระหว่างอัตราอินเทอร์เฟซต่าง ๆ

• 32 long-reach (LR) 112G PAM4 SerDes พร้อมความสามารถในการตั้งโปรแกรมเพื่อเพิ่มประสิทธิภาพพลังงานเทียบกับประสิทธิภาพการทำงาน

• รองรับสาย DAC รวมถึงการเจรจาอัตโนมัติ (auto-negotiation) และการฝึกเชื่อมโยง (link training)

• ใช้งานได้กับค่าอุณหภูมิของอุตสาหกรรม ทำให้ปรับใช้ในสภาพแวดล้อมกลางแจ้งได้

• Complete Software Development Kit (SDK) ที่สมบูรณ์พร้อมความสามารถในการอัปเกรดแบบสม่ำเสมอและ warm restart นอกจากนี้ยังเข้ากันได้กับ META-DX1 SDK ที่ได้รับการพิสูจน์แล้วในภาคสนาม

ไมโครชิพนำเสนอชุดการออกแบบหลักที่ทำงานร่วมกันแบบอ้างอิงสำหรับการออกแบบและแผงประเมินผล เพื่อช่วยลูกค้าในการสร้างระบบ ด้วยอุปกรณ์ META-DX2L นอกจากเทคโนโลยี Ethernet PHY แล้วไมโครชิพยังมีเครื่องมือ เช่น PolarFire® FPGAs PLL ประสิทธิภาพสูง ZL30632 ออสซิลเลเตอร์ ตัวควบคุมแรงดันไฟฟ้า และส่วนประกอบอื่น ๆ ที่ได้รับการตรวจสอบแล้วว่าสามารถทำงานร่วมกับ META-DX2L ได้ เพื่อช่วยให้ผู้ออกแบบระบบสามารถนำการออกแบบไปผลิตได้รวดเร็วยิ่งขึ้น

ความพร้อมของผลิตภัณฑ์: ในระยะแรกเราคาดว่าอุปกรณ์ META-DX2L จะถูกสุ่มตัวอย่างในช่วงไตรมาสที่สี่ของปี 2564 สำหรับข้อมูลเพิ่มเติม โปรดไปที่หน้าเว็บ PM6200 META-DX2L หรือติดต่อตัวแทนฝ่ายขายของไมโครชิพ

แหล่งที่มา: ภาพการใช้งานความละเอียดสูงสำหรับสื่อเพื่อเผยแพร่: www.flickr.com/photos/microchiptechnology/51374945989/sizes/l/